AI chips push shift to multi-die packaging

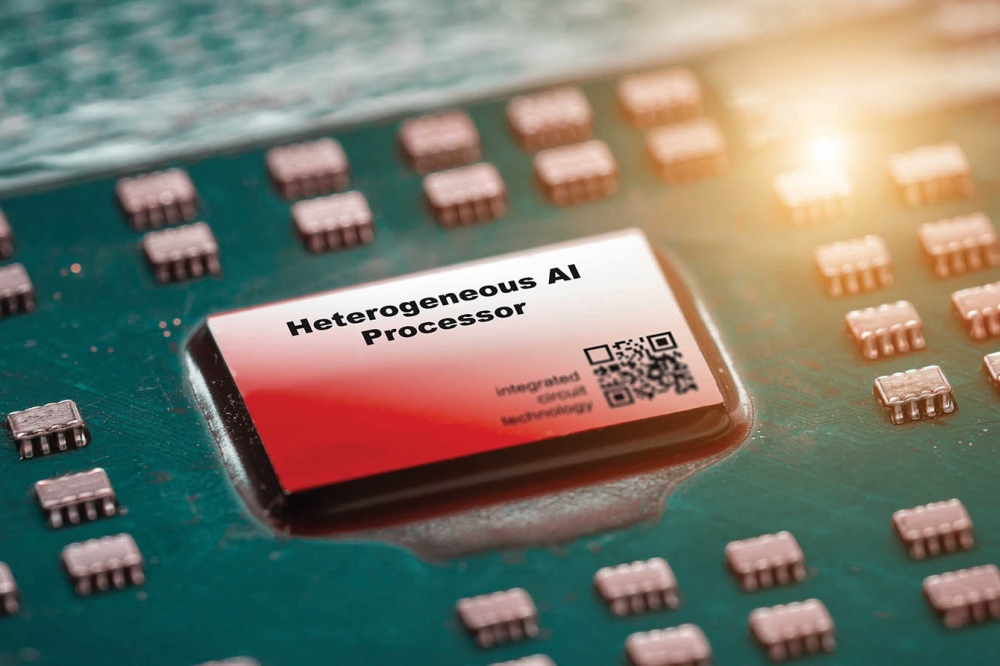

Rising design complexity is accelerating the adoption of chiplets and advanced packaging across AI semiconductors.

A new white paper from Synopsys highlights how the rapid growth of artificial intelligence is driving a fundamental shift in chip design toward multi-die architectures and advanced packaging solutions.

As AI workloads expand across industries, both startups and established semiconductor companies are developing increasingly large and complex chips to accelerate algorithms and improve efficiency, putting pressure on traditional monolithic designs.

Multi-die and chiplet-based approaches are emerging as a preferred strategy, enabling higher compute performance, reduced communication overhead, and improved power efficiency.

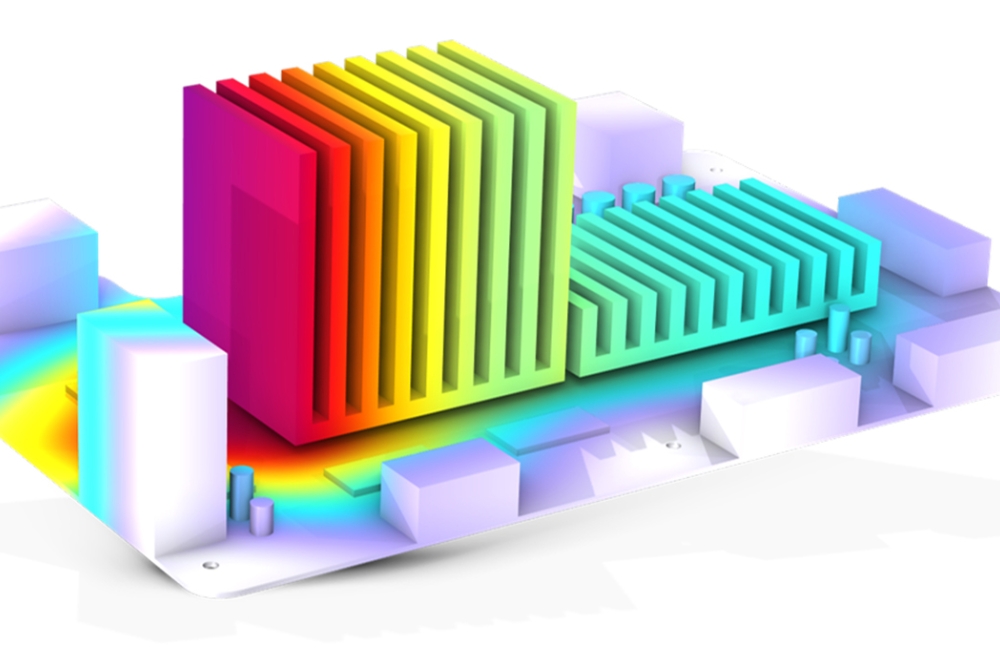

This shift is closely linked to the rising importance of advanced packaging technologies, which enable high-bandwidth, low-latency interconnects between dies and support heterogeneous integration.

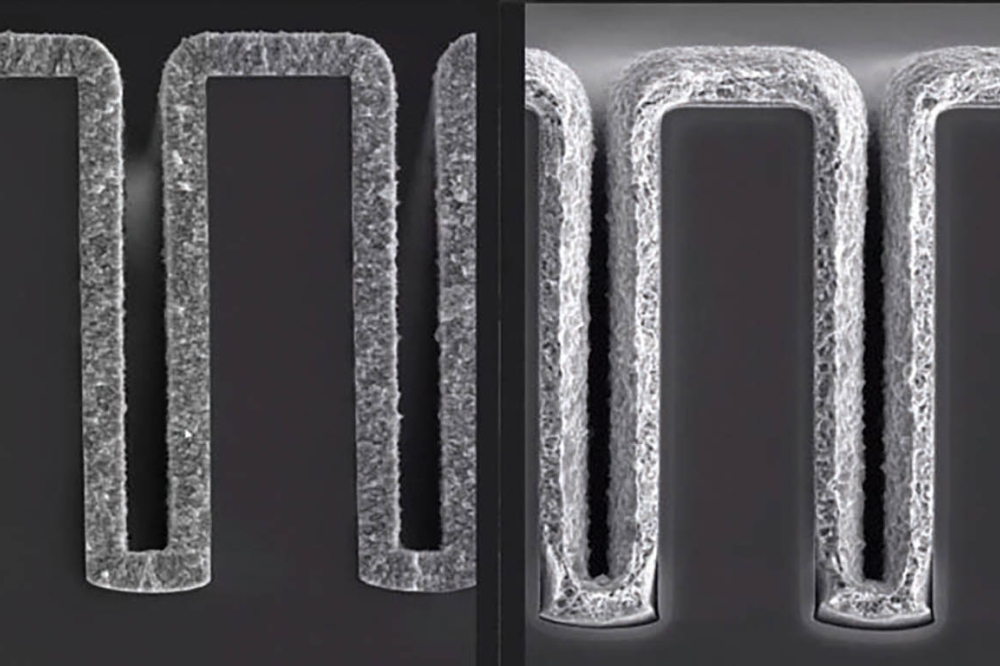

The report points to growing adoption of 2D, 2.5D, and 3DIC packaging approaches as essential to next-generation AI systems, allowing designers to scale performance beyond single-die limits.

It also notes that developing such chips requires specialised tools and methodologies across both silicon design and packaging stages, with tighter integration between the two becoming increasingly critical.

As AI continues to reshape semiconductor requirements, advanced packaging is moving to the centre of the design process, underpinning the industry’s shift toward more complex, high-performance architectures.