Beyond Moore’s Law: Packaging as the new frontier

As Moore’s Law slows, advanced packaging is emerging as the key driver of semiconductor performance and innovation.

For more than half a century, Moore’s Law has defined the trajectory of the semiconductor industry, enabling continuous gains in performance, cost, and integration. But as scaling approaches both physical and economic limits, the industry is entering a new phase—one where progress is increasingly determined not just by smaller transistors, but by how chips are integrated and connected.

In this conversation, Phil Alsop, Contributing Editor at Advanced Packaging Magazine, speaks with Lee Chee Ping of Lam Research about the growing importance of advanced packaging, the role of AI in accelerating adoption, and the technical and ecosystem challenges shaping the future of semiconductor innovation.

PA: Moore’s Law has driven the semiconductor industry for decades. Why is it no longer sufficient?

LCP: Moore’s Law has been incredibly successful, allowing us to double transistor density over decades while improving performance and reducing cost. It enabled the transition from large personal computers to laptops and now to powerful smartphones.

But scaling is becoming more difficult. Moving to nodes like 2nm and beyond is not only technically challenging but also significantly more expensive.

If you think of a chip as a house and transistors as rooms, we’ve been trying to fit more rooms into the same footprint. But there’s a limit—you can’t shrink those rooms indefinitely, and the cost of that “real estate” keeps rising.

So the question becomes: how do we continue increasing functionality? That’s where advanced packaging comes in. Instead of expanding laterally, we’re building vertically—more like constructing a skyscraper than extending a single-storey building.

PA: What trends are pushing the industry toward advanced packaging?

LCP: Artificial intelligence is fundamentally changing system requirements. Training large models demands enormous compute capability, which means processors and memory need to be integrated much more closely.

Advanced packaging enables this. Technologies like interposers and Through-Silicon Vias allow chips to be placed closer together, reducing latency and energy consumption.

If you imagine two houses far apart, moving data between them takes time and energy. But if those houses are stacked in a skyscraper and connected by a high-speed elevator, everything becomes faster and more efficient.

That’s what advanced packaging delivers—not just performance, but also improvements in power efficiency and system-level optimisation.

PA: What kinds of next-generation technologies will this enable?

LCP: Advanced packaging is evolving in two directions.

One is 3D stacking, where we pack more chips together vertically to increase compute density—essential for high-performance AI systems.

The other is scaling at the package level, integrating many chiplets into a single large package for exascale computing.

It may seem contradictory that we’re both miniaturising and scaling up, but packaging is flexible. Hyperscale AI systems need large, powerful packages, while consumer devices like AR glasses demand extreme miniaturisation. Both rely on advanced packaging.

PA: How is packaging evolving at the manufacturing level?

LCP: One key shift is from wafer-level to panel-level packaging. Traditional wafers are circular, which creates inefficiencies when placing rectangular chiplets.

By moving to panel formats—like 300mm by 300mm or larger—we can improve utilisation and reduce cost. This is especially important for large AI packages, where maximising the number of integrated dies is critical.

PA: Why is Asia so dominant in advanced packaging?

LCP: Asia has built a strong semiconductor ecosystem over the past 30 to 40 years. Today, most AI chips are fabricated and packaged in the region.

High-bandwidth memory comes from Korea, while processors and packaging are handled by leading foundries in Taiwan. Early investment in technologies like CoWoS has also given the region a first-mover advantage.

Equally important is ecosystem depth—alignment across supply chain, talent, capital, and infrastructure. Advanced packaging is now recognised as a core enabler of performance, not just a back-end process.

PA: How important is advanced packaging at a strategic level?

LCP: It’s extremely important. Governments worldwide are investing heavily in semiconductor capabilities, including packaging.

Singapore is strengthening R&D infrastructure, Malaysia is scaling packaging capacity, Japan is investing in next-generation technologies, and India is emerging as a future growth region.

For companies across the value chain—foundries, memory players, and OSATs—advanced packaging is now central to their roadmap.

PA: What are the main technical challenges in 3D stacking?

LCP: There are several. One is the stacking approach itself—die-to-wafer versus wafer-to-wafer bonding.

Die-to-wafer bonding introduces gaps that must be filled, which can create mechanical stress. As more layers are added, the stress increases and can lead to cracking.

Wafer-to-wafer bonding requires extremely flat surfaces, but processing steps can introduce warpage. Techniques like backside stress compensation help restore flatness.

There are also productivity challenges—working at the micron scale requires high-throughput solutions.

PA: How are yield and cost challenges being addressed?

LCP: As chip value increases, the cost of failure becomes significant.

That’s why equipment intelligence is critical. We’re integrating sensors and inline metrology to monitor processes in real time, allowing us to detect issues early and prevent yield loss.

PA: How do engineers balance performance, reliability, and manufacturability?

LCP: It depends on the application.

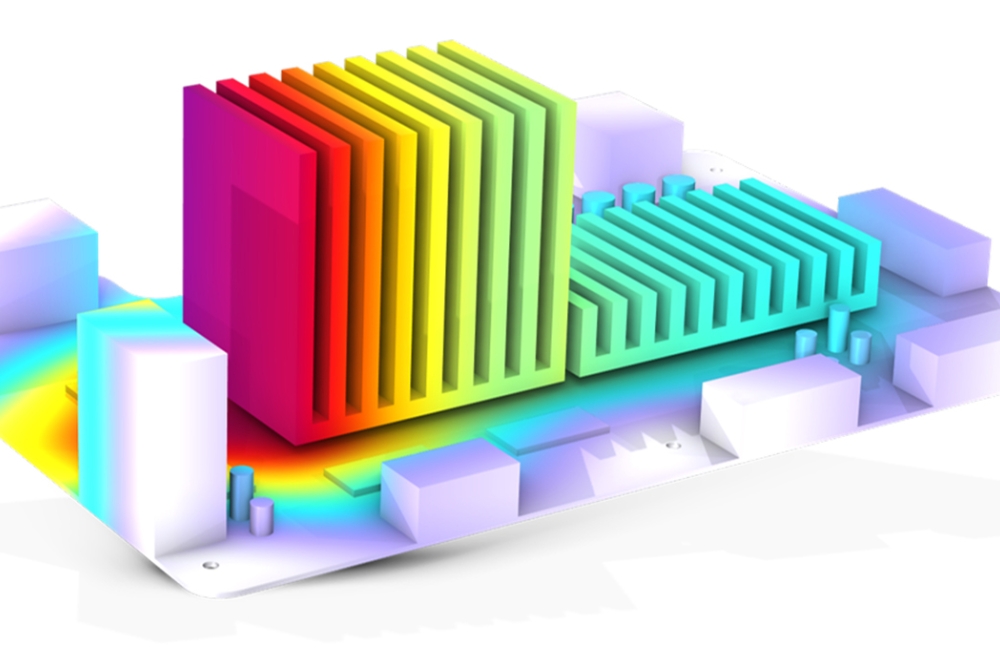

In homogeneous stacking, like high-bandwidth memory, we’re already stacking up to 16 layers, with plans to go further. Thermal and mechanical stability are the main challenges.

In heterogeneous integration, communication between different chiplets becomes critical. Standards and interconnect technologies play a key role.

There’s no single solution—it requires collaboration across the ecosystem.

PA: Which innovations are most critical?

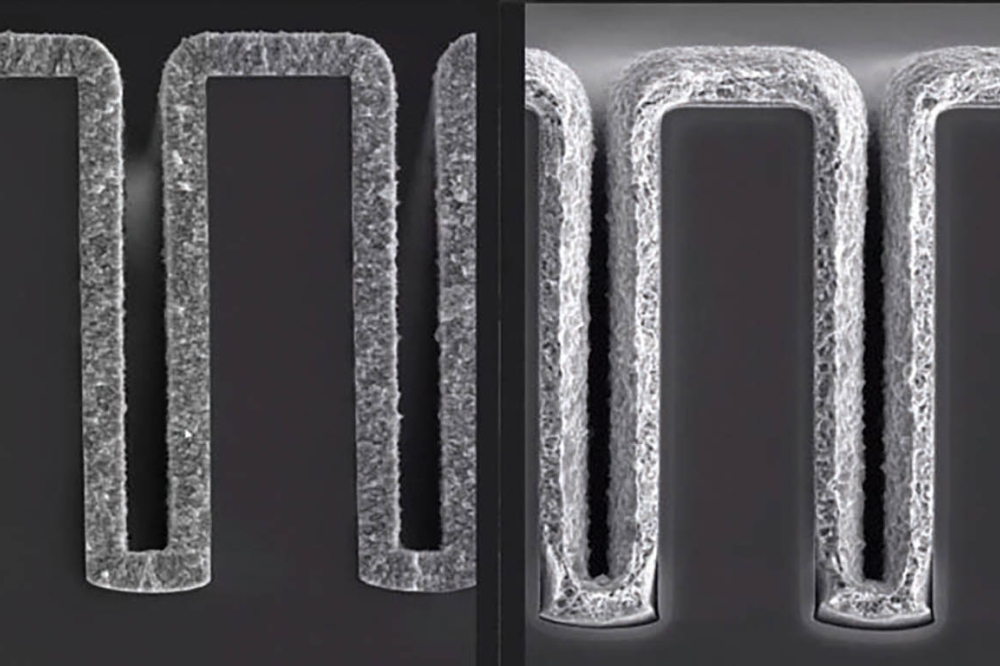

LCP: Fine-pitch interconnects and high-aspect-ratio TSVs are essential as we increase I/O density.

We also need multiple via sizes within the same chip—larger ones for power delivery, smaller ones for signal transmission.

Hybrid bonding is another major innovation, enabling direct chip-to-chip connections without traditional bumps, improving both density and performance.

PA: How is the supply chain adapting?

LCP: The supply chain is evolving rapidly. Foundries and OSATs are expanding into advanced packaging, while new entrants are bringing innovative models.

Packaging also offers more accessible entry points compared to leading-edge fabrication, creating opportunities for startups and increasing ecosystem dynamism.

PA: How will advanced packaging reshape the industry?

LCP: The biggest shift is in how the industry operates.

Traditionally, development followed a linear path—design, fabrication, packaging, assembly. Now, these stages are becoming integrated and must be developed in parallel.

System integration is the central challenge, combining logic, memory, photonics, and more into a single package.

No single company can solve this alone—it truly takes an ecosystem.

PA: Finally, what does this shift toward advanced packaging mean for the future of semiconductor innovation?

LCP: Advanced packaging represents a fundamental shift in how the industry continues to scale performance. As traditional transistor scaling approaches its limits, innovation is increasingly being driven by integration—how we bring different components together into a single, highly efficient system.

It is also enabling the rapid growth of AI and other compute-intensive applications, where performance, power efficiency, and system-level optimisation are critical.

Ultimately, the future of semiconductors will not be defined solely by smaller transistors, but by smarter integration. Advanced packaging is becoming the new centre of innovation.