ALD: Interfacial engineering to enable high performing package architectures

Atomic layer deposition quietly enabled the high-k era. Now AI-compute and extreme aspect-ratio interconnects demand atomic control again - at scale. Advances in deposition technology reveal that semiconductor winners will master interfacial control, not just dimensions

Tyler J. Myers, PhD, Senior Technical Sales Engineer, Forge Nano, Inc.

Atomic layer deposition (ALD) rarely gets top billing in semiconductor headlines. It is the kind of technology that does its most important work out of sight. Yet if you trace the industry’s most pivotal inflection points, ALD keeps showing up as a critical enabler to realize next-generation devices.

Since Gordon Moore uttered his eponymous law, scaling was a story of shrinking – how can we fit more precious chips on a wafer? The obsession with smaller transistors, tighter pitches and higher density drove the semiconductor industry’s technology development, including the first adoption of ALD for logic manufacturing. That era is not over, but it is no longer the full picture. The performance and energy demands of AI-era compute, coupled with heterogeneous integration carrying a growing share of system-level innovation, have pushed the industry toward a new reality: The next winners will not be defined solely by who shrinks the fastest at a reasonable yield. They will be defined by who controls matter most precisely - at the atomic level - and who can do it at scale.

ALD: the “quiet enabler” of miniaturization

ALD became essential long before it gained any notoriety. When Intel introduced high-k dielectrics to their manufacturing line in 2007 they demanded uniformity and defect control that conventional deposition struggled to deliver.

The sequential, self-limiting ALD method provided the process control needed to fabricate thin, conformal and pinhole-free films. ALD provided a route to much thinner gate oxides, and ultimately devices with lower power consumption, enabling Intel’s transition from the 65 to 45nm node.

Figure 1. Illustrative schematic of the ALD process. Material is deposited using sequential reactions that react only until all surfaces sites are saturated, resulting in precision thickness control, 100% step coverage, and high-quality materials

Today, a similar dynamic is repeating, but the challenge is many-fold. As device architectures are becoming increasingly complex, the traditional scaling conversation has moved to the package, and the performance demands are outpacing what systems can currently deliver.

This complexity requires the optimisation of more than size; it requires the strict control of every material, and in consequence, every interface, down to the nanometre. At those bounds, small deviations are more than noise. A few nanometres of non-conformal barrier at a critical junction, a thermal interface with too large non-uniformity or a void that becomes an electromigration hotspot, can spell disaster.

Packaging is becoming the architecture

Innovation in the advanced packaging space primarily involved ways to protect the die and route signals outward. Back-end-of-the-line (BEOL) work was generally seen as a separate set of fabrication steps. Now the package architecture increasingly defines performance. The systems driving AI acceleration and high-bandwidth memory no longer rely on a single monolithic chip. They rely on many chips with varying functions connected in close proximity, with massive interconnect density and tight power/thermal constraints.

As primary integration strategies like chip-on-wafer-on-substrate (CoWoS) and other 2.5D/3D approaches become mainstream, the interconnect stack begins to look more like front-end scaling than back-end assembly. Through-silicon vias (TSVs), through-glass vias (TGVs), and fine-pitch redistribution layers must support higher I/O counts, lower latency, and better signal integrity without sacrificing yield.

This is where deposition physics becomes strategic. To raise interconnect density, vias and trenches are pushed toward higher aspect ratios (AR), i.e. a feature’s height divided by its width. But as AR increases, conventional, directional deposition methods struggle.

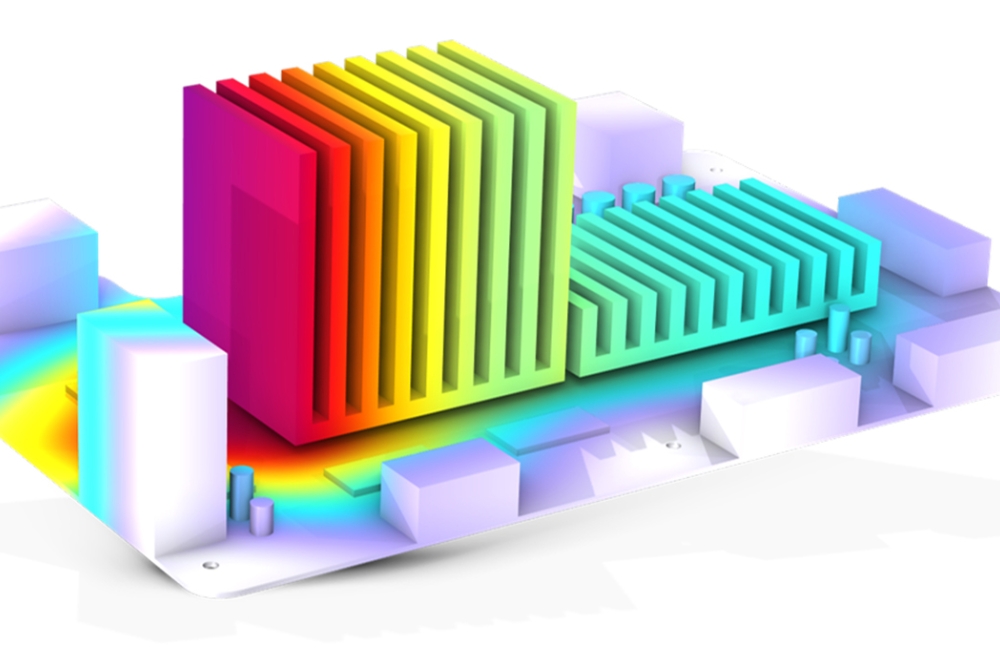

Figure 2. Illustrative surface coverage examples of physical vapor deposition (PVD) and atomic layer deposition (ALD). PVD tends to have higher deposition rates with a trade-off in uniformity. ALD-grown materials are 100% conformal and uniform due to its self-limiting nature

Line-of-sight processes, particularly physical vapour deposition (PVD), can lose effectiveness at surprisingly modest aspect ratios. In practice, many PVD approaches fail above ~10:1, and in some cases even lower.

The result can be a chain reaction of manufacturability issues:

- Non-conformal barriers inviting copper diffusion

- Poorly uniform seed layers preventing robust electroplating

- Voids and pinch-off driving yield loss and reliability risk

With packaging becoming synonymous with new device architectures, reliable interconnect fabrication is one of the new choke points.

The atomic-control requirement

It is tempting to treat advanced packaging challenges as a sole matter of making features narrower. But at high ARs and high-performance demands, it becomes harder to deliver the right material at the right thickness, throughout the entire structure.

The problems become more complicated than just, “Do I have a solution to enable via filling?” They now include:

- Can I deposit seeds conformally from top to bottom?

- Can I create the conditions for void-free electrodeposition in extreme structures?

- Can I keep interfaces chemically stable and electrically reliable?

- Can I do all of this without consuming too much via volume?

Those questions are fundamentally answered by atomic-level control. And ALD excels when it is engineered to meet manufacturability constraints.

The barrier/seed bottleneck: where packaging scaling gets stuck

In today’s high-density interconnects, copper remains a workhorse of metal. But copper brings an old problem into a new geometry: it needs a diffusion barrier to prevent electromigration into underlying substrate, and a seed layer that supports smooth, continuous electrodeposition. In deep, narrow features, successful barrier/seed deposition is not guaranteed and decides whether the copper plates cleanly or fails.

Traditional approaches relied on PVD stacks. However, as aspect ratios rise, PVD struggles to maintain continuity, suffering from thickness non-uniformity. The failure modes are familiar to those in high-AR metallisation: poor adhesion, large void formation, and top-heavy deposition profiles.

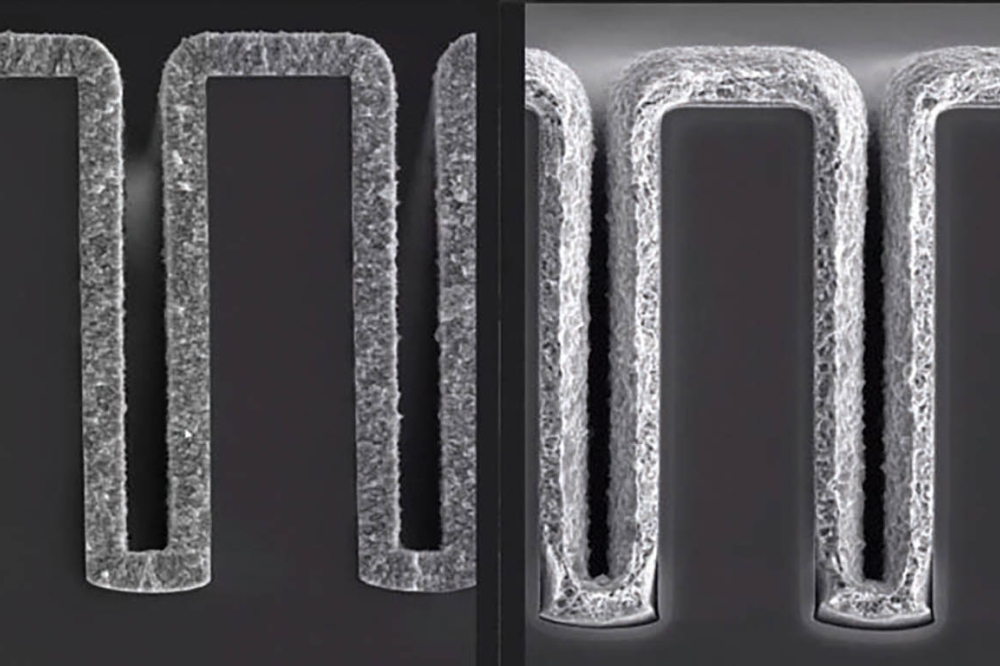

Figure 3. Copper electrodeposition in 4:1 AR blind silicon vias utilizing (left) ALD-coated SiO2/TiN/Ru barrier/seed and (right) PVD-coated Ti/W barrier/seed. Numerous voids, trench narrowing and bread-loafing is visible when plating on a PVD seed layer

Already, it is easy to see that ALD can solve the baseline functional problem with higher AR interconnects. Even at aspect ratios as low as 4:1, attempted copper electrodeposition on PVD barrier/seed layers in blind silicon trenches show familiar failure mechanisms. The copper grown on an ALD stack enables clean, uniform, and void-free electrodeposition due to ALD’s ability to grow materials conformally in any geometry.

ALD, however, doesn’t just enable functional electrodeposition. It can improve the entire stack through precision thickness control and careful material selection.

Let’s take Forge Nano’s all-thermal metal barrier/seed solution as an example of how ALD redefines what is manufacturable for interconnect fabrication.

What an ALD barrier/seed stack enables

Forge Nano has devised a metal barrier/seed stack comprised of all-thermal grown SiO2, TiN and Ru for promotion of conformal, void-free copper electrodeposition in TSVs and TGVs (only TiN and Ru for TGVs).

Figure 4.~100nm barrier/seed deposited by ALD on a blind Si via. The film is highly conformal with 100% step coverage and excellent uniformity at the trench corner and on the Bosch scallops. Cu adheres well and conformally on the Ru seed layer

A conformal ALD stack addresses the scaling and performance bottleneck in four practical ways:

- All-thermal ALD supports higher AR - Thermally-grown ALD films mean the deposition conformality is not limited by geometry. This ensures the roadmap to high AR and high-density interconnect structures is not constrained by the barrier/seed layer.

- Ultrathin barrier/seed films preserve via volume - In high-AR structures, every nanometre counts. A thick, non-uniform barrier/seed stack consumes valuable space, raising overall resistance. ALD’s precision thickness control offers thinner films that free up volume for the conductive fill. The narrower the via, the more important fine thickness control becomes, especially in high density vias where copper also helps with thermal management.

- Low-resistivity metals improve overall electrical outcome - When the barrier and seed become a meaningful fraction of the cross-sectional area, their resistivity matters. Low resistivity materials grown by ALD, like TiN and Ru, can create an interconnect pathway with higher overall conductivity than stacks that rely heavily on higher-resistivity layers. These materials will become crucial for enabling the superconducting needs of interconnects in quantum computing applications.

- 100% step coverage enables, conformal and void-free copper electrodeposition - Copper electroplating reveals where the seed is continuous and where it is not. With conformal ALD barrier/seed layers, copper nucleates and grows uniformly, reducing void formation and pinch-off risk in vias and trenches.

This barrier/seed stack has been demonstrated on silicon and glass vias exceeding 35:1 aspect ratio, with the goal of enabling next-generation packaging interconnects where directional deposition fails.

Figure 5. Electrodeposition of Cu on Forge Nano’s ALD barrier/seed in 10:1 AR TGVs. The copper starts plating conformally on all surfaces, then begins filling from the middle of the via and proceeds symmetrically to fill the entire via, free from voids, narrowing or bread-loafing

Figure 6. Horizontal trenches with starting AR of 330:1 were coated conformally with ALD and production-competitive speeds. As the gap narrows, chemical was being transported to the bottom of the trench with effective aspect ratios of 1000:1. Images courtesy of C2Mi

For packaging audiences, the headline is straightforward:

If you want to move to the 30:1–35:1 AR regime and beyond, atomic-level control of your interfaces becomes the deciding factor for yield and reliability.

And that brings us to the most important part of the ALD conversation: can it scale?

Why ALD faced resistance

It is tempting to talk about ALD as though it is inevitable. What’s not to love about atom-by-atom control? In practice, ALD spent much of its history on the margins because everything else was faster and cheaper.

For many layers, directional deposition and other high-throughput approaches delivered “good enough” films at a fraction of the cost and cycle time. ALD, by contrast, came with very real adoption barriers: slower deposition rates, purges and exposures that stretch dramatically in high aspect-ratio features, and process trade-offs between precursor utilisation and throughput.

The result was an industry mindset that treated ALD as a last resort. In other words, a tool you reached for only when the fast, economical options had unequivocally run out of road.

Advanced packaging in the AI-era is changing that mindset. As interconnect densities increase, “good enough” films are no longer viable. The problem remains, though, that the industry can absorb higher process cost when the alternative is yield, reliability and roadmap risk, but the throughput tax can be more difficult to accept.

Which raises the real question for the next era: if the winners are truly those who control matter the most precisely, how is it possible to stay ahead if the costs are ballooning?

Breaking the deposition bottleneck

This is where process innovation matters as much as deposition principle.

Forge Nano’s patented ALDx approach targets the practical bottlenecks that historically limited ALD adoption in production contexts, particularly at high aspect ratio. Rather than treating ALD as a slow but perfect process, the goal is to deliver ALD-quality films with manufacturing-relevant efficiency.

In Forge Nano’s metal barrier/seed work, the toolset focuses on fast dosing and rapid cycling, using clever valve and chamber design optimised to deliver throughputs rivalling traditional processes with orders of magnitude less precursor consumption.

With single-wafer deposition rates as high as 12 nm/min and precursor usages 100x lower, it becomes realistic to think of ALD as an architecture-enabling platform technology for advanced packaging, rather than a niche process reserved for only the most unforgiving geometries.

That shift matters because it separates two futures:

- One where packaging scaling stalls because deposition cannot keep up with manufacturing needs

- Another where packaging becomes a design space where engineers can push architectures without worry that execution is impossible due to OPEX constraints

A wider lens: from 35:1 interconnects to 1000:1 structures

Thus far, we have anchored the packaging narrative at a bottleneck being addressed today: barrier/seed metallisation and the 35:1 interconnect regime that challenges directional deposition.

But advanced packaging is not limited to TSVs and TGVs. The same interplay can be extended to other packaging aspects that will show up across the package in new ways.

One compelling example is deep trench capacitors, where surface area translates to charge storage. The ability to conformally coat deeper trenches without defects translates to higher capacitance in the same footprint. Forge Nano has shown turbulent-flow capability that can coat aspect ratios up to 1000:1, with production-level robustness, and that result has been independently validated by Canadian research institute, C2Mi.

This is not a claim that packaging will become 1000:1 overnight. It is, however, a signal that the industry’s assumed limits are moving quickly, and that deposition constraints once treated as immovable can become engineering problems with practical solutions.

The AI race is becoming an atomic engineering race

So, the truth is laid bare: the most meaningful performance gains now do not come from another geometry shrink. They come from system architecture and the reliability of the materials that make that architecture manufacturable. That means the competitive advantage shifts.

In the next generation:

- Some teams will optimise routing and assembly around deposition limits.

- Others will change the limits by innovating the materials and interfaces that define those processes.

The second group wins more than yield; they win freedom. They can:

- Push interconnect density higher

- Reduce resistance and improve signal/power integrity

- Enable architectures competitors cannot easily copy

ALD will not be the only tool in that toolbox, but it will be what you reach for when you need atomic control, conformality, and repeatability in critical structures.

ALD’s second act will be louder than the first

ALD helped enable the high-k era without demanding the spotlight. Advanced packaging in the AI-era may change that.

As interconnect aspect ratios climb and heterogeneous integration becomes a core lever for system performance, the industry needs deposition approaches that do not compromise film quality or interface control. At the same time, those approaches must be compatible with scale because “it works in a lab” does not win markets.

The next generation of semiconductors will reward those who can innovate at the atomic level and deliver that innovation through manufacturable processes. That is where ALD moves from a quiet enabler to a competitive separator.

Atomic precision is not a slogan. It is becoming the price of admission.