Forge Nano targets AI packaging

Sarab Chopra, Editor of Advanced Packaging Magazine, speaks with Tyler J. Myers, Technical Sales Engineer at Forge Nano Inc., about how atomic layer deposition is helping semiconductor manufacturers tackle extreme aspect ratios, improve via performance, and meet the rising demands of AI-era packaging.

As advanced packaging becomes increasingly central to system performance, semiconductor manufacturers are under pressure to support higher-density interconnects, deeper vias, and more complex 3D architectures. For Forge Nano, that shift is creating new opportunities for atomic layer deposition (ALD), particularly where conventional deposition techniques begin to hit their limits.

In this interview, Tyler J. Myers explains how Forge Nano is positioning its ALD technology for advanced packaging, why AI is accelerating demand for more precise thin-film processes, and where he sees the next wave of innovation emerging across materials, thermal management, and heterogeneous integration.

SC: Could you start with a brief overview of Forge Nano and its role in the semiconductor and advanced packaging space?

TJM: Forge Nano is a U.S.-based semiconductor equipment and advanced materials company focused on atomic layer deposition. We work across both AI-era chip manufacturing and defence battery applications through a platform we call Atomic Armour.

On the semiconductor side, our focus is on a proprietary ALD approach that uses turbulent flow rather than the more conventional laminar-flow process. That allows us to coat extremely complex semiconductor structures quickly and efficiently while maintaining the precision ALD is known for.

We offer a tool platform called ALDx, built around an all-thermal, single-wafer approach. Compared with traditional laminar cross-flow ALD reactors, our system is significantly faster and far more chemically efficient, while also delivering the conformal coating performance needed for advanced packaging.

That is especially important as the industry moves toward higher-aspect-ratio structures in redistribution layers, silicon and glass interposers, and other 3D packaging schemes. As those geometries become deeper, narrower, and denser, manufacturers need atomically precise thin films with full step coverage and high film quality. That is where we see Forge Nano contributing.

SC: What are the key challenges in advanced packaging that Forge Nano is trying to address?

TJM: One of the biggest challenges today is scaling through-wafer vias. In through-silicon vias and through-glass vias, you typically need a material stack that acts as a liner before conductive fill can be deposited. In silicon, for example, that might include a dielectric layer, then a barrier film such as tantalum nitride or titanium to prevent copper diffusion, followed by a seed layer to support copper electrodeposition.

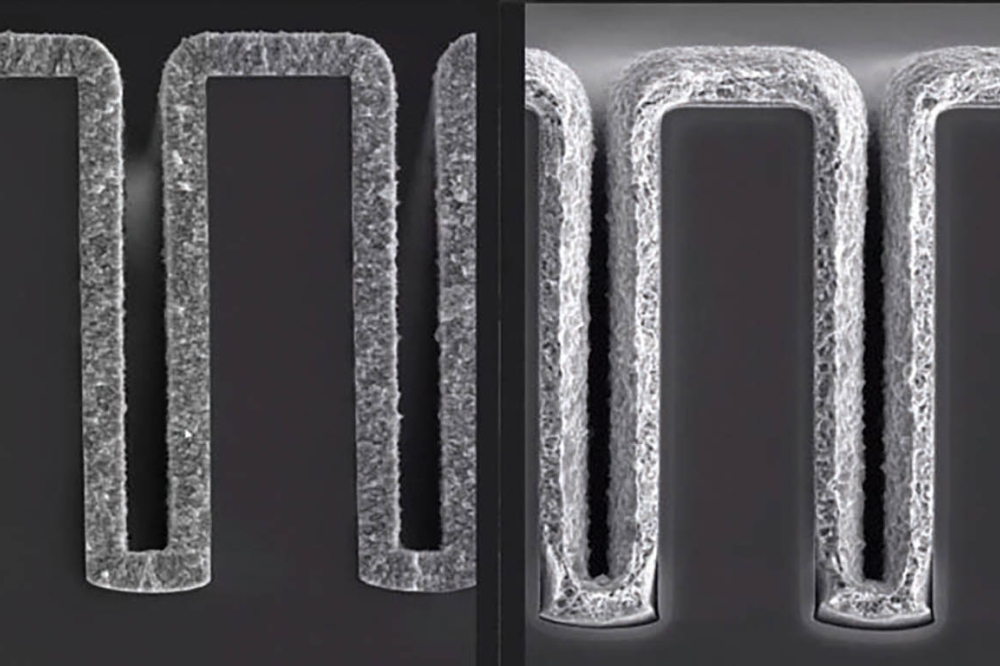

The problem is that many of these layers are still deposited using directional methods such as PVD, or in some cases, plasma-enhanced ALD. These approaches become limiting when aspect ratios increase, because they do not coat deep, narrow features uniformly. Material tends to build up near the top of the trench, which can create narrowing, poor fill behaviour, and ultimately voids or unreliable vias.

ALD is different because it is isotropic. It deposits the same amount of material across the full surface, even in very deep or highly complex structures. In principle, that means there is no hard aspect-ratio limit — it becomes more a question of process time.

That is where our turbulent-flow method becomes important. It enables us to move gases efficiently into and out of very deep structures, which helps maintain production-worthy throughput. We have demonstrated barrier and seed stacks on aspect ratios of 35:1 and above, on both silicon and glass, along with void-free copper fill.

There is also a performance benefit. In the AI era, every bit of via volume matters. If you can reduce liner thickness while keeping excellent control and film quality, you leave more room for the conductive fill that actually carries the current. Beyond that, ALD also opens the door to better-engineered liner stacks using materials that actively improve via performance rather than simply acting as passive layers.

SC: How is demand evolving as AI and high-performance computing continue to scale?

TJM: Demand is rising quickly. What we are seeing now is that package architecture is becoming just as important to performance as device scaling itself. It is no longer enough to focus only on transistor performance. The package has to keep pace as well.

That is why advanced packaging is starting to look more like front-end scaling than traditional back-end processing. OSATs, foundries, and IDMs are all being pushed to adopt more precise, more controllable manufacturing strategies.

In that environment, ALD is very well positioned. Historically, ALD became a critical enabler when the device industry reached a major scaling inflection point — Intel’s move from 65nm to 45nm was a landmark moment in that transition. I think advanced packaging is approaching a similar point now, where ALD becomes essential not as an optional enhancement, but as a real enabler of future package architectures.

SC: What recent developments or innovations from Forge Nano are you most excited about?

TJM: One of the most exciting areas for us is the work we recently highlighted on extreme-aspect-ratio structures. With our turbulent-flow ALD approach, we have shown conformal film deposition in structures with aspect ratios as high as 1,000:1, and at speeds that are competitive for production.

That is significant because, while ALD has always been theoretically capable of coating deep features, in practice, the challenge has been doing it fast enough for manufacturing. Our approach lets us efficiently introduce chemistry into those structures and then quickly transition to purge conditions, which helps keep cycle times low.

A very promising application is deep trench capacitors. In those devices, performance scales directly with aspect ratio: the deeper the trench, the more surface area you have, and the more capacitance you can achieve. The ability to deposit metals and insulators uniformly inside ultra-deep trenches creates a strong opportunity for next-generation capacitor designs.

We are also excited about our catalysed ALD work. Traditionally, ALD has been divided into thermal and plasma-enhanced processes. Plasma can help drive reactions, but it also introduces limitations, especially in deep features where recombination effects can become problematic. Our catalysed approach lowers the activation barrier through surface chemistry, allowing certain materials to be deposited thermally with only a very small amount of catalyst.

That is a concept that has existed in research for a long time, but it has been difficult to turn into something practical for manufacturing. One thing Forge Nano does well is take ideas that have been seen as interesting but commercially difficult, and engineer them into viable industrial processes.

SC: How do you see advanced packaging evolving over the next few years?

TJM: I think we are heading toward a real materials arms race. Package architecture alone will not be enough to deliver the performance required by AI and high-performance computing. Every material in the package will have to be engineered more carefully.

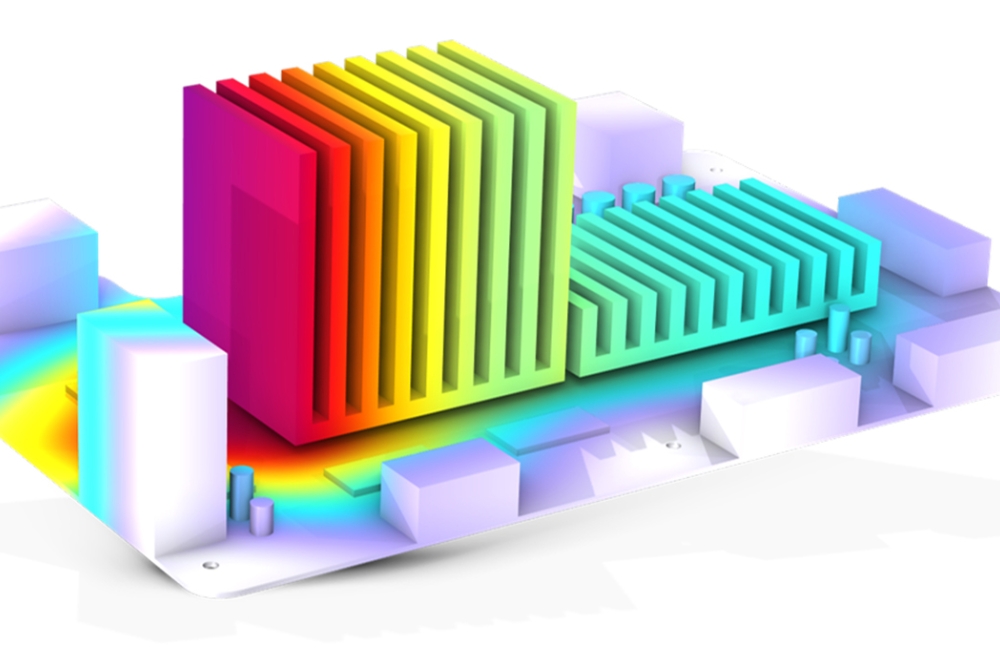

That includes interconnect materials, where the industry is already exploring alternatives to copper, as well as thermal management materials. Heat removal is becoming one of the defining constraints in advanced packaging. Materials such as diamond and aluminium nitride are especially interesting because of their thermal properties, and I think there will be growing focus on how to prototype, integrate, and scale these kinds of materials quickly.

At the same time, heterogeneous integration will remain a major theme. Co-packaged optics is one particularly interesting direction, because the industry is steadily pushing more functionality closer together in the package. The challenge will be achieving that density while still managing thermal budgets and maintaining manufacturability.

I also think the design process itself will change. Package engineering can no longer be treated as an afterthought. In the future, package engineers will need to work alongside device designers from the outset, shaping architecture decisions at the same time as the silicon itself is being defined.

SC: What are you most looking forward to discussing at the Advanced Packaging Conference?

TJM: I am especially interested in how the commercial landscape is going to evolve. As advanced packaging becomes more tightly tied to overall system performance, the traditional separation between front-end device manufacturing and back-end assembly starts to break down.

That has major implications for OSATs, foundries, and IDMs. For years, OSATs have played a defined role in the backend, but now their expertise and intellectual property are becoming much more strategic. That raises interesting questions: Will foundries look to bring packaging capability in-house? Will there be more mergers and acquisitions? Or will OSATs find new ways to remain independent while leveraging their growing technical value?

Those are the kinds of conversations I expect to become increasingly important, because advanced packaging is no longer a side discussion. It is becoming central to semiconductor competitiveness.