TSMC CoWoS pricing nears 7nm

Rising demand for AI chips is pushing advanced packaging into a high-margin, strategic role within the semiconductor supply chain.

TSMC is seeing its CoWoS (Chip-on-Wafer-on-Substrate) advanced packaging technology reach new levels of strategic and commercial importance, as demand from AI applications continues to surge.

According to reports citing Commercial Times, the average selling price (ASP) of a CoWoS wafer has climbed to around $10,000, approaching the level of leading-edge 7nm process nodes.

The pricing reflects both strong demand and tight supply, positioning CoWoS as one of the most constrained resources in the AI semiconductor supply chain.

With relatively lower capital expenditure requirements compared to advanced front-end nodes, CoWoS is also emerging as a potentially high-margin business.

While margins for advanced packaging currently sit below the company’s overall average, they are expected to improve as capacity scales and utilisation increase.

Advanced packaging accounted for roughly 10% of TSMC’s revenue in 2025, with that share projected to grow further amid continued AI-driven demand.

Industry estimates suggest CoWoS capacity could reach approximately 1.3 million units in 2026 and expand to 2 million units by 2027.

Alongside capacity expansion, TSMC is advancing its packaging roadmap.

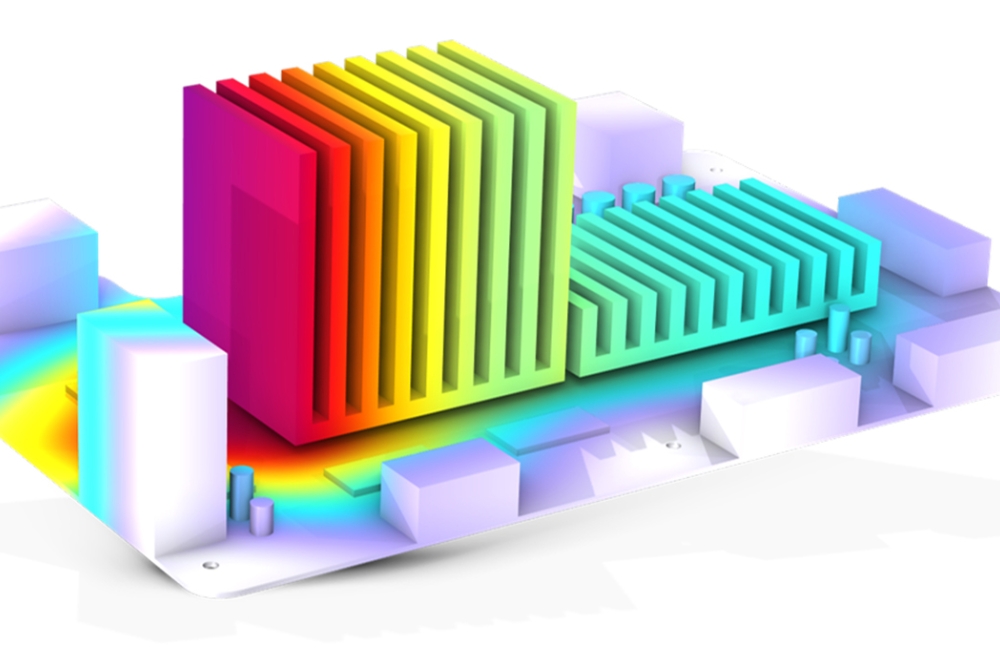

At its 2026 North America Technology Symposium, the company outlined plans to scale CoWoS to larger reticle sizes, enabling integration of more compute dies and high-bandwidth memory (HBM).

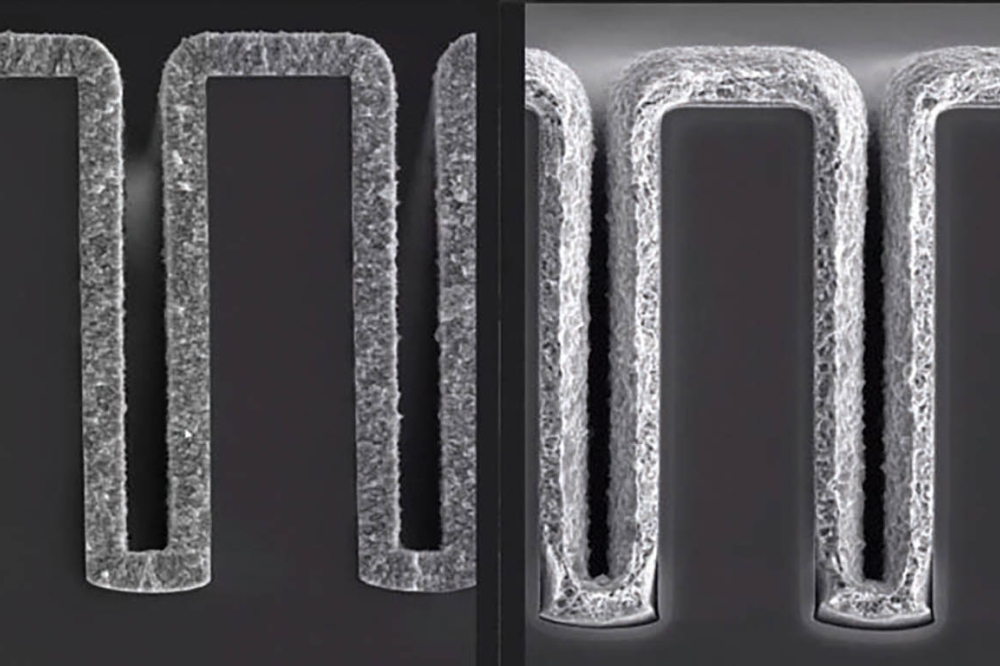

It is also advancing its 3D stacking technologies, including SoIC, and developing co-packaged optics (CPO) solutions for future high-performance computing systems.

The developments highlight how advanced packaging is evolving from a supporting process into a central competitive lever in the race to deliver next-generation AI hardware.